New World

[디지털논리회로#14, 15] 기억장치와 PLD 본문

기억장치의 개요

기억장치

- 주기억장치 + 보조기억장치

- 처리할 프로그램과 데이터를 기억하거나 처리한 후의 결과를 기억하는 장치

- 단어 (2진 기억소자의 모임, 2진 비트들의 조합) : 2^n개의 비트, 위치는 주소로 부여

- 성능 : 액세스 타임(기억장치의 정보를 읽거나 기록하는 속도)에 좌우

- 반도체 메모리 : F/F 회로를 실리콘 칩에 고밀도로 집적화 (RAM/ROM)

- PLD : 읽기만 가능한 기억장치 (PLA, PAL)

RAM(Random Access Memory/RWM)

- 휘발성 메모리

- 임의의 기억장소에 사용자가 작성한 프로그램이나 데이터를 저장

- 필요할 때마다 그 내용을 읽어낼 수 있으며 자유롭게 변경

- SRAM : F/F로 구성, 고속의 액세스 타임, 캐시 메모리로 사용

- DRAM : 커패시터로 충전(refreshing)되는 전하의 형태로 정보 저장, 주기억장치로 사용

|

- 데이터 입,출력선 : 저장시킬 정보를 저장장치에 전달, 외부장치로 내보내기 - 주소선 : 기억장치 내의 단어를 선택 - 제어선 : 쓰기는 정보 -> 기억장치 / 읽기는 정보 -> 외부 - 기억장치 규모 : 저장할 수 있는 단어의 수와 각 단어를 구성하는 비트 수 2^k x n (단어수 x 비트) |

|

- 메모리 셀(기억소자) + 디코딩 회로 (단어선택) - 메모리 셀 : F/F회로로 구성, RAM 구성의 기본 단위 - 선택 단자(E) : 기억소자 선택 - 읽기/쓰기 단자 : 기억소자에 대한 읽기/쓰기 모드 결정 R/W = 1 : 읽기 모드, F/F와 출력단자 사이에 경로를 형성하여 출력 R/W = 0 : 쓰기 모드, 입력단자로 F/F로 경로를 형성하여 기억 기억부 : 여러 개의 메모리 셀, 2차원의 테이블 or 행렬 해독부 : 디코더, 기억장치 선택입력에 의해 구동 제어부 : 읽기/쓰기 단자의 입력신호에 따라 데이터 입출력을 제어 |

RAM 확장

- 개개의 RAM을 서로 연결하면 더 큰 용량의 기억장치 구성

기억용량 증가

- 단어의 수 증가 : 주소선의 비트 수를 늘려 단어를 선택하는 주소의 길이를 증가

- 비트 수 증가 : RAM을 병렬 연결

ROM(Read Only Memory)

- 고정된 2진 정보를 저장, 기록되어 있는 데이터를 읽어낼 수만 있는 기억장치

- 내용 변경 X, 전원 끊어도 내용 소멸 X

- 디코더와 여러 개의 OR 게이트로 구성 => 내부의 전자 퓨즈선으로 구성, 전원 유무에 상관 없이 유지

- 마스크 ROM : 한번 저장한 것은 내용 변경 X

- PROM : 사용자가 데이터를 써 넣을 수 있는 프로그래밍이 가능

- EPROM : 한번 쓴 내용 지우기 가능

|

|

|

|

- K개의 입력이 디코더로 2^k개의 디코더 출력 중 하나가 1 - 디코더 출력이 메모리 배열 중 1개의 단어를 출력, 단어의 비트들이 출력단자에 나타남 |

|

PLD의 구조와 종류

PLD

- 프로그램이 가능한 전자 퓨즈선으로 연결된 게이트의 배열로 구성된 집적 회로

- AND 게이트와 OR 게이트의 배열 구조

- 논리요소들이 배열 형태로 내부 연결선을 프로그래밍

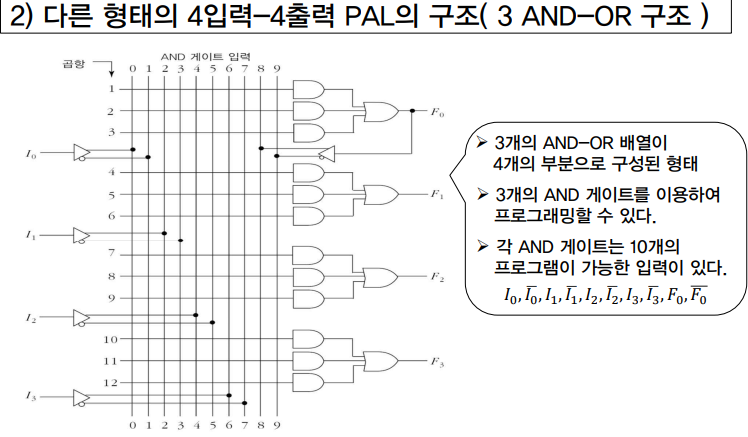

| PLA | PAL |

| - ROM과 같은 기능 수행, 단점을 해소 - 모든 입력변수를 디코딩 X, 모든 최소항도 만들지 X |

- AND 게이트 배열만 프로그래밍 - 싼 값, 간단한 논리함수 구현 |

|

|

| PLA를 이용한 부울함수 - PLA 내부를 구성하는 AND-OR 배열을 프로그래밍 - 조합논리회로의 논리를 나타내는 PLA 프로그래밍 표 작성 |

PAL 를 이용한 부울함수 - AND 게이트 배열만 프로그래밍 |

|

|

'Self-Study > Study' 카테고리의 다른 글

| [방통대] 정리집 | 이산수학 (0) | 2022.05.26 |

|---|---|

| [방통대] 정리집 | 컴퓨터 보안 (0) | 2022.05.25 |

| [디지털논리회로#12, 13] 레지스터와 카운터 (0) | 2022.05.22 |

| [디지털논리회로#9,10,11]순서논리회로 (0) | 2022.05.22 |

| [디지털논리회로#6,7,8]조합논리회로 (0) | 2022.05.21 |